It makes

sense to avoid exposure to electrical shock.

While some sources are expected to have a possible dangerous impact, others

of quite high potential are of limited current and are sometimes held in less

regard.

External in/output

PC ANALOG

INPUT, PC DIGITAL INPUT, PC AUDIO INPUT, HEADPHONE OUTPUT, COMPONENT 1

INPUT,COMPONENT2INPUT, S-VIDEO INPUT, TUNER,VIDEO OUTPUT (Audio In : 0.4Vrms,

over 10KΩ

Video In :

1Vp-p, over 75Ω)

Sound output

10W+10Wrms

Stereo (Max)

Part appearance

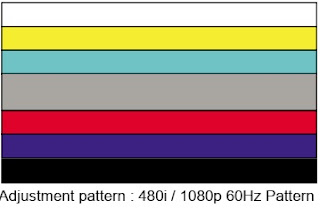

ADJUSTMENT INSTRUCTION WITH DEFAULT

FACTORY DATA

Service mode data adjustment

When the EEPROM has been

replaced, the SVC data should be restored as the function of individual system

and specification.

When the EEPROM has been replaced White Blance Checking.

Enter and exit SVC mode. Into the SVC mode, Initialize with default data.

1) Press 5

Seconds MENU buttons on both TV set and Remote Controller at the same time to

get into SVC mode.

2) Press the PR ▲▼ button several

times to find SVC Data.

3) Input the corresponding SVC data

referring to Table below with the VOL ◀▶ , key.

4) Press TV/AV button to exit SVC

mode.

White balance checking

The TFT LCD TV described

in the followings is based on a Multi TV system, digital Control display,

23.01" diagonal. The TFT LCD TV is intended to be a finished product,

Basically a display device mounted inside an enclosure which will provide the

safety Requirements. With the exception of LCD Panel, the display device shall

be composed entirely of solid state components.

These components shall have a history of reliable service in identity

applications and shall be applied in the circuits.

SCALER SECTION.

VCT 49xxi SECTION.

Video A/D Converter

The MST6151 is a high

performance and fully integrated graphics processing IC solution for

multi-function LCD monitor/TV with resolutions up to SXGA/WXGA. It is

configured with an integrated triple-ADC/PLL, an integrated DVI/HDCP receiver,

a video de-interlacer, two high quality scaling engines, an on-screen display

controller, and a built-in output clock generator. By use of external frame

buffer, PIP is provided for multimedia applications. It

supports de-interlaced full-screen video, video-on-graphic overlay,

video-by-graphic split screen, frame rate conversion, and aspect ratio

conversion for various video sources. To further reduce system costs, the

MST6151 also integrates intelligent power management control capability for

green-mode requirements and spread-spectrum support for EMI management.

The VCT 49xxI is an IC

family of high-quality singlechip TV processors. Modular design and

deep-submicron technology allow the economic integration of features in all classes

of singlescan TV sets. The VCT 49xxI family is based on functional blocks

contained and approved in existing products like DRX 396xA, MSP 34x5G, VSP

94x7B, DDP 3315C and SDA 55xx.

Each member of the family contains the entire IF, audio, video, display, and

deflection processing for 4:3 and 16:9 50/60-Hz mono and stereo TV sets. The

integrated microcontroller is supported by a powerful OSD generator with

integrated Teletext & CC acquisition including on-chip page memory.

Video A/D Converter

Most flat-panel monitors

and projectors require a digital graphics input in order to accurately scale

and display graphics. The huge installed base of computers with analog video

graphics interfaces necessitates the use of a graphics digitizer to re-digitize

the analogue RGB signal before further processing.

■ The MST9883CR is a fully integrated analog interface for digitizing

high-resolution RGB graphics signals from PC’s and workstations. With a

sampling rate capability of up to 140 MHz, it can accurately support display

resolutions up to 1280x1024 (SXGA) at 75 Hz. The clamped input circuits provide

sufficient band width to accurately digitize each pixel.

■ The MST9883CR provides a high performance highly integrated solution to

support the digitization process, including the ADC’s, a voltage reference, a

PLL to generate the pixel sampling clock from HSYNC, clamping circuits, and

programmable offset and gain circuits to provide brightness and contrast

controls.

■ When the COAST signal is asserted, the PLL will maintain its output frequency

when HSYNC pulses are absent, such as during the VSYNC period in some systems.

■ A 32-step programmable phase adjustment control (0-360 deg) is provided for

the pixel sampling clock to adjust for the difference between the HSYNC edge

and RGB pixel edge timing.

■ The MST9883CR can send output data through one 24-bit port at the pixel clock

rate.

■ The MST9883CR can also support RGB to YCbCr conversion.

■ The MST9883CR has internal programmable pattern generator for testing.

■ The MST9883CR can accept either standard TTL, CMOS levels or saw tooth

vertical deflection signals for VSYNC input.